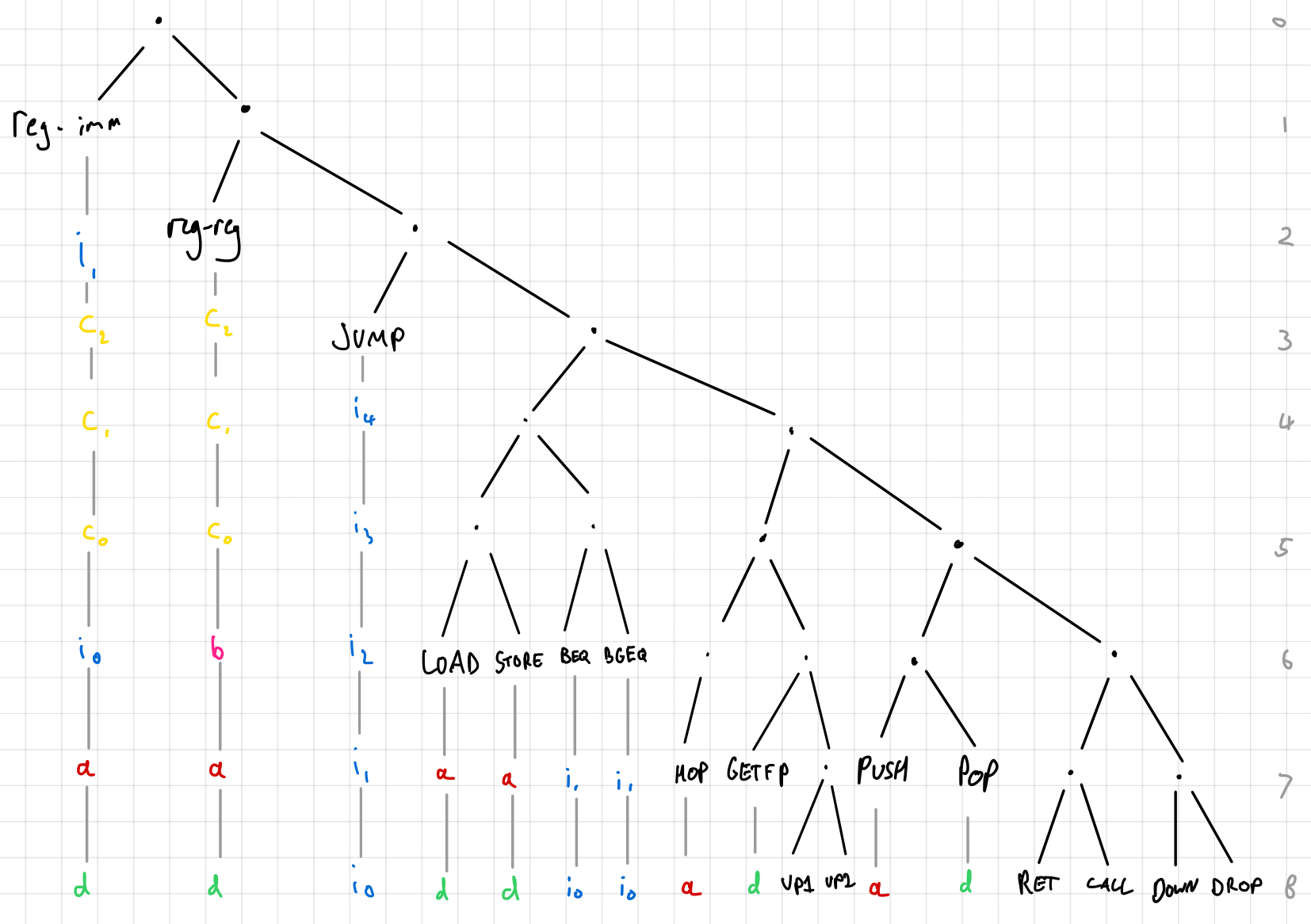

Phase 1 - ISA Design

Reg-imm and reg-reg instruction codes:

| Code | Operation | Info |

|---|---|---|

| 000 | ADD | Addition: a + b |

| 001 | SUB | Subtraction: a - b |

| 010 | AND | Bitwise AND: a & b |

| 011 | OR | Bitwise OR: a | b |

| 100 | XOR | Bitwise XOR: a ^ b |

| 101 | LLS | Logical left shift: a << b |

| 110 | LRSZ | Logical right shift zero/unsigned: a >>> b |

| 111 | LRSS | Logical right shift signed: a >> b |

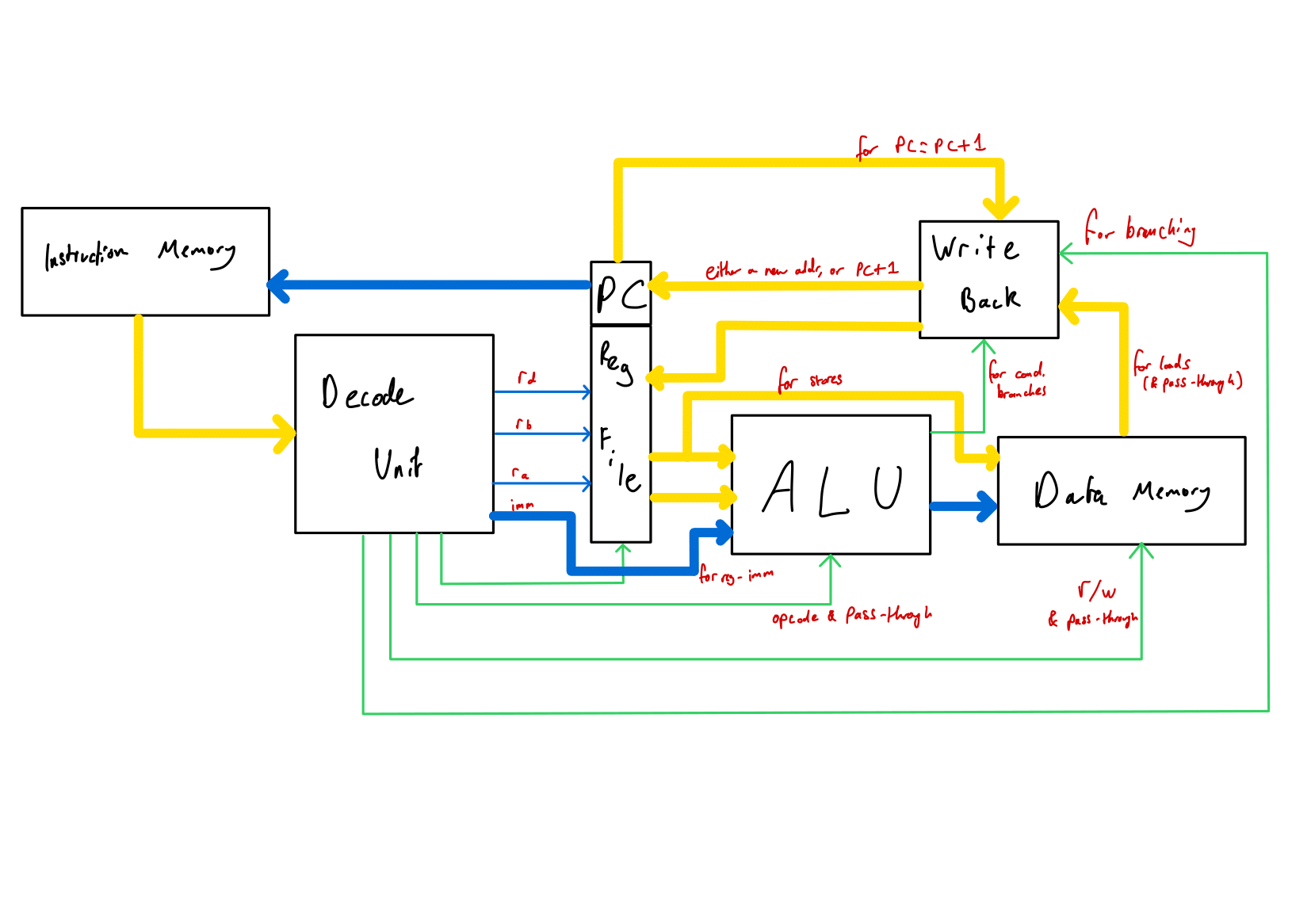

Phase 2 - High-Level Implementation Design

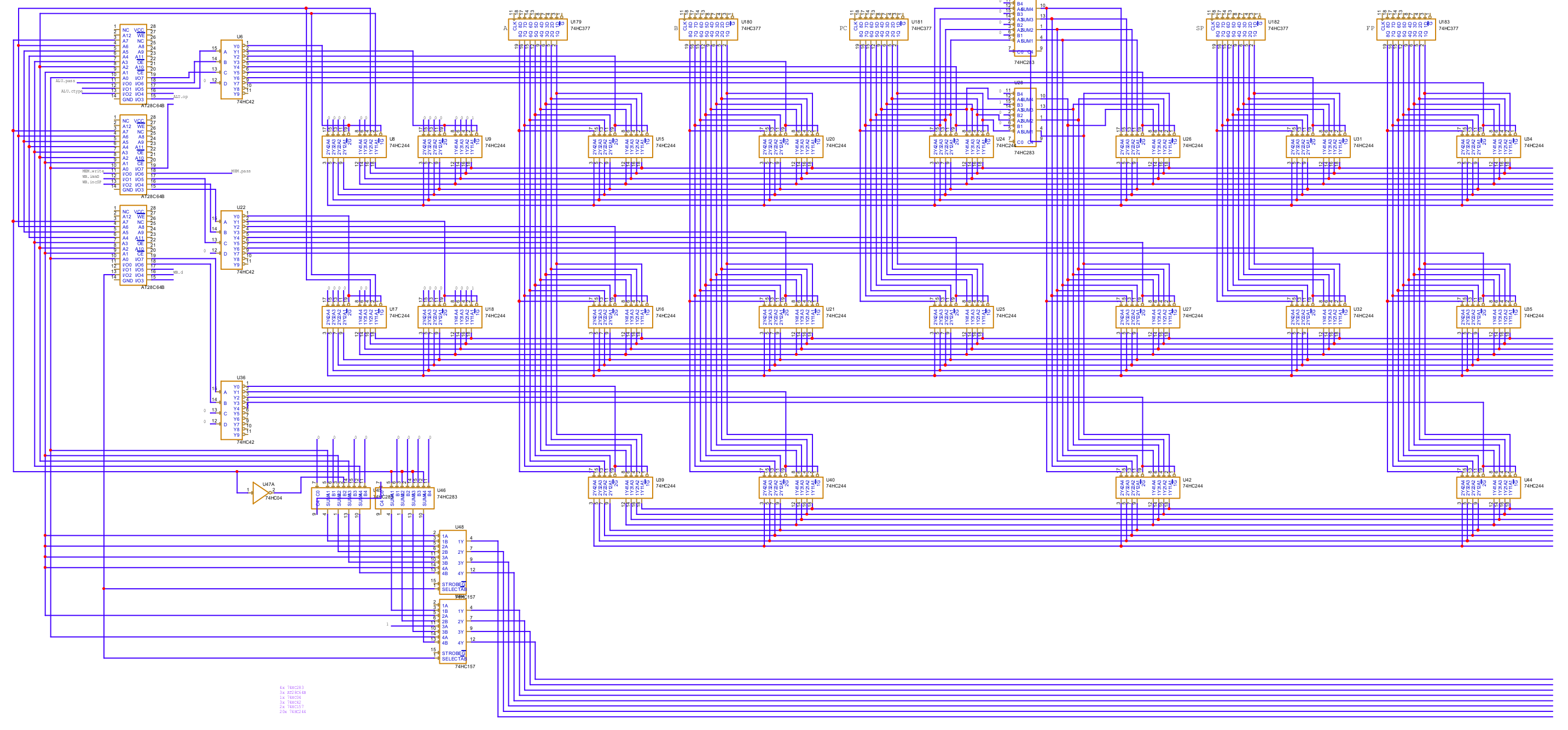

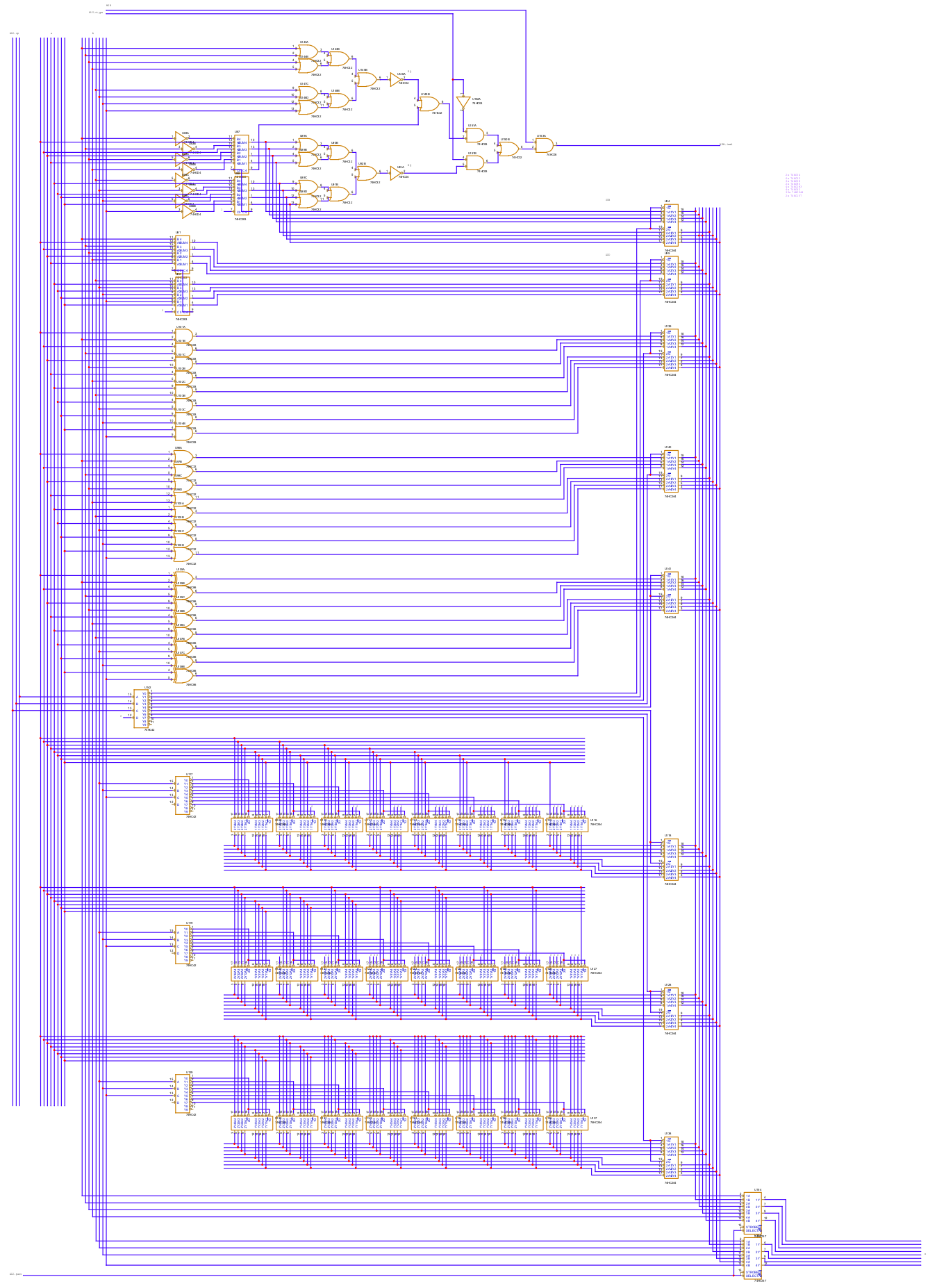

Entire CPU

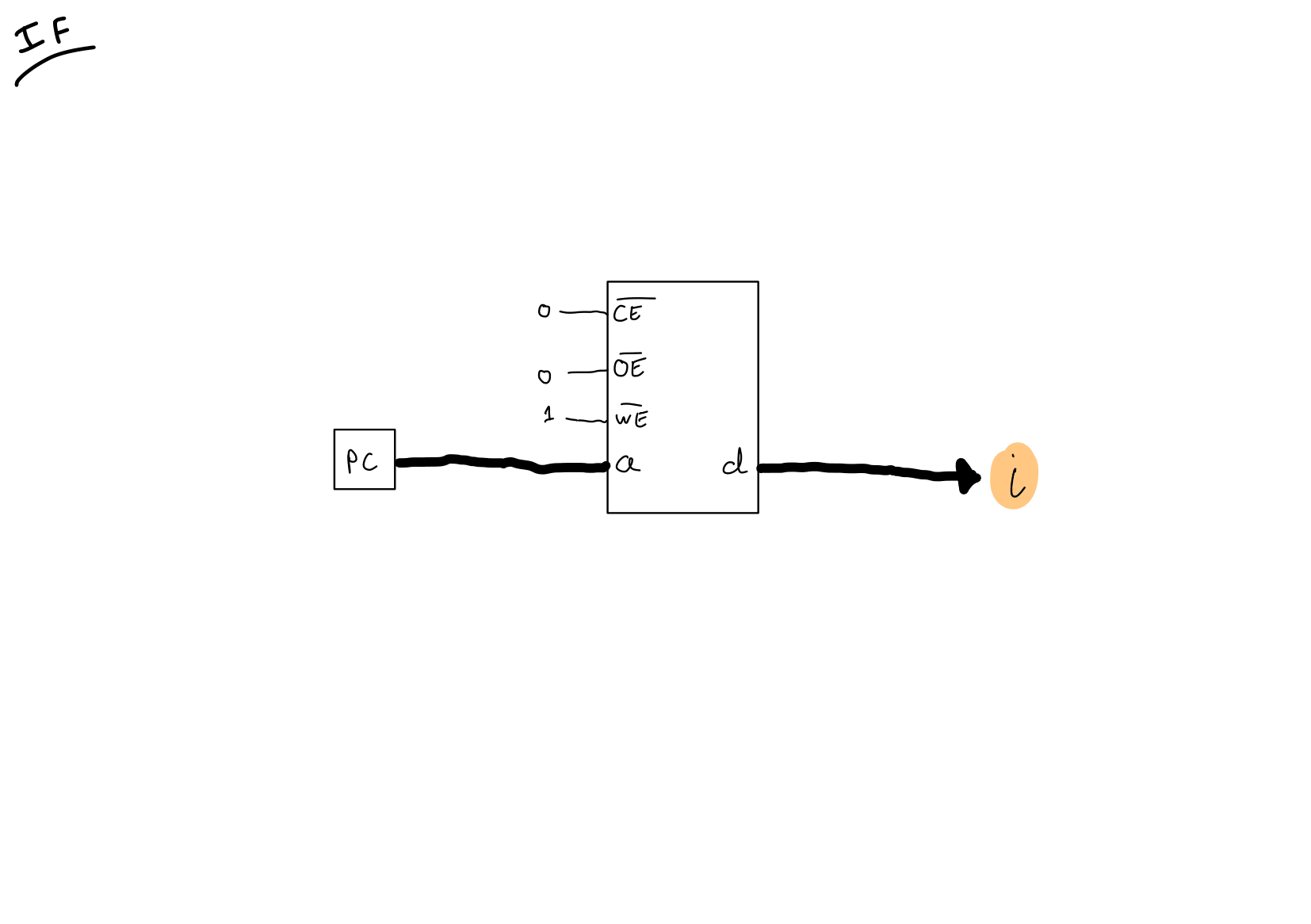

Instruction Fetch (IF)

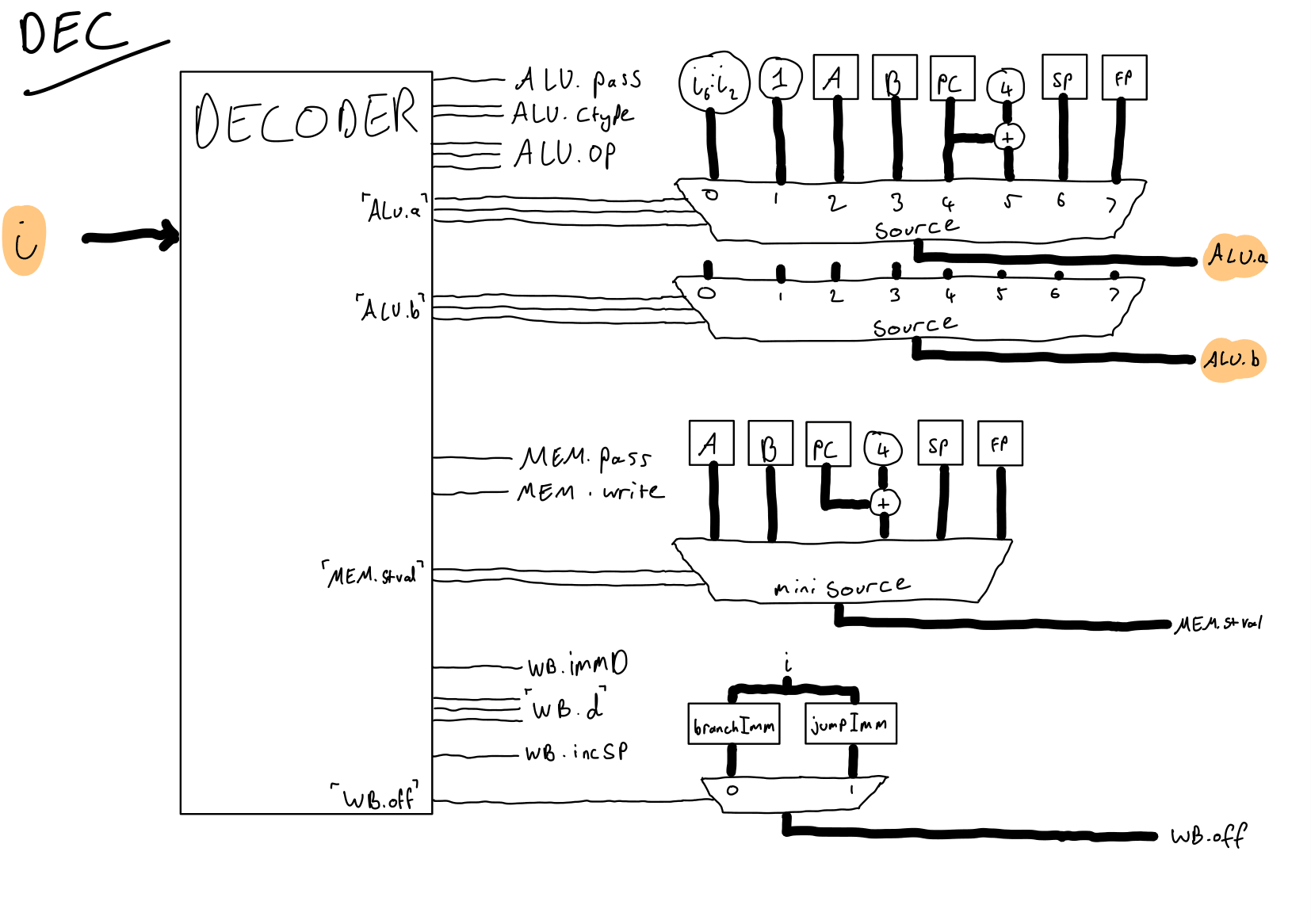

Instruction Decode (DEC)

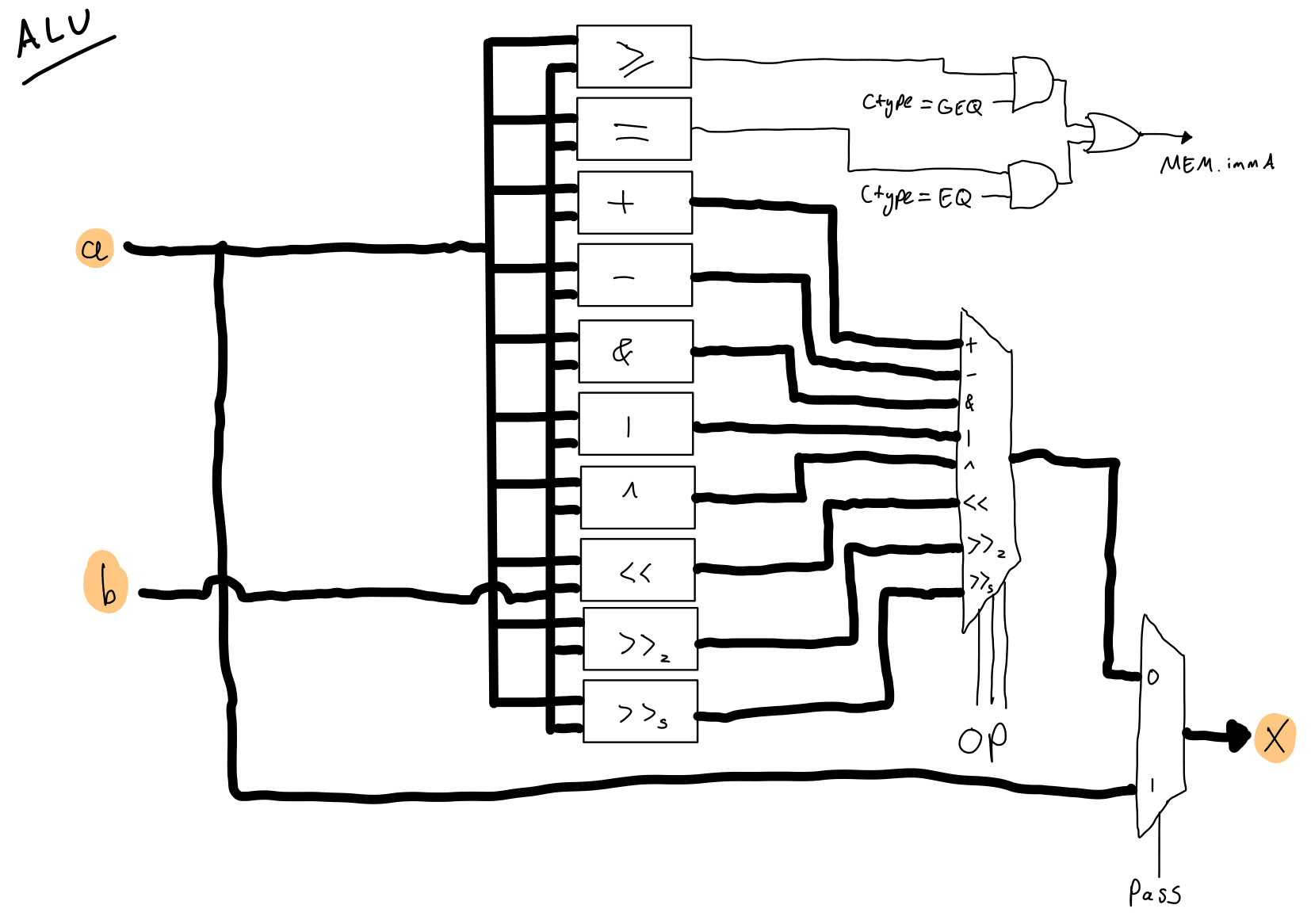

Arithmetic Logic Unit (ALU)

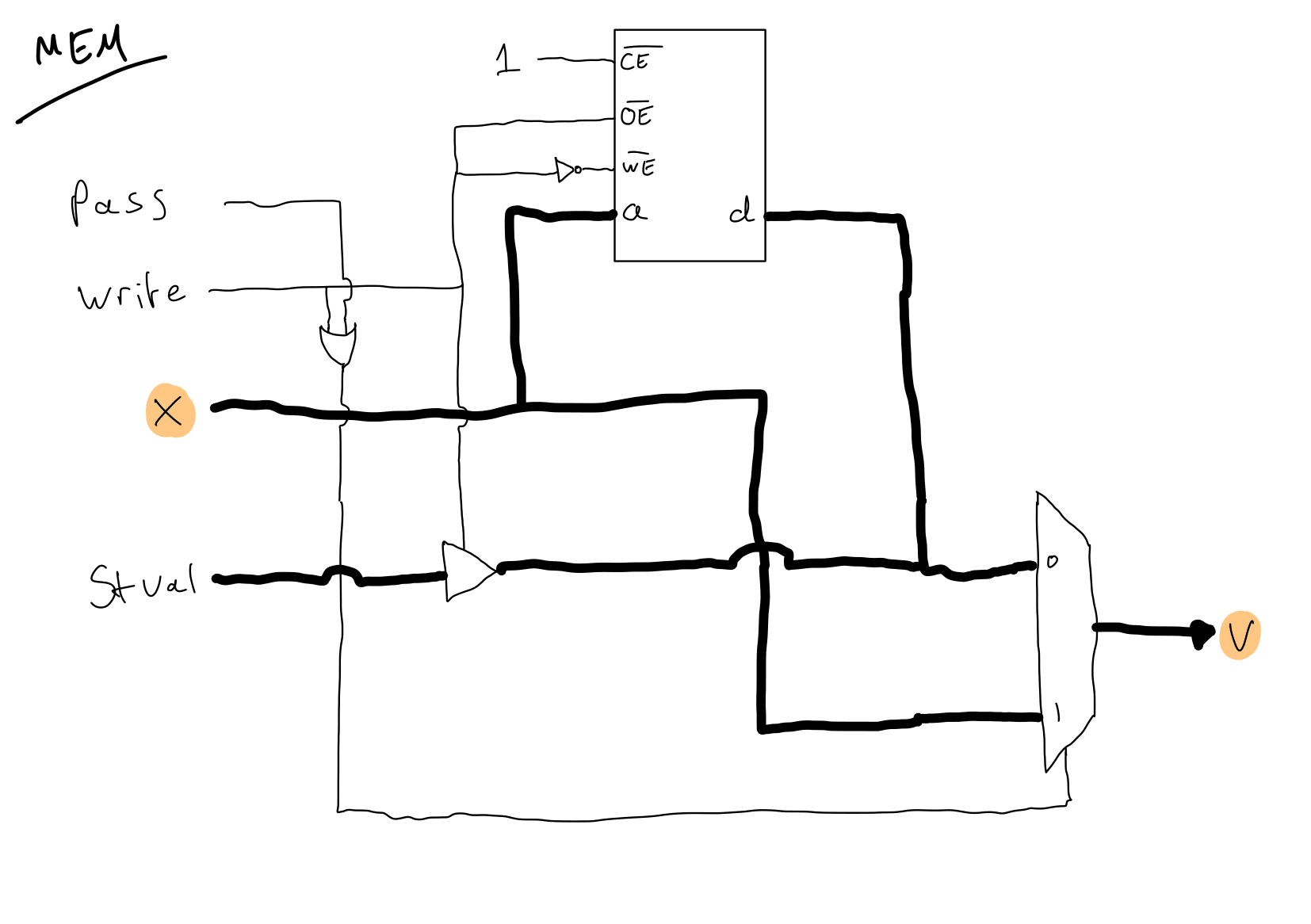

Data Memory Access (MEM)

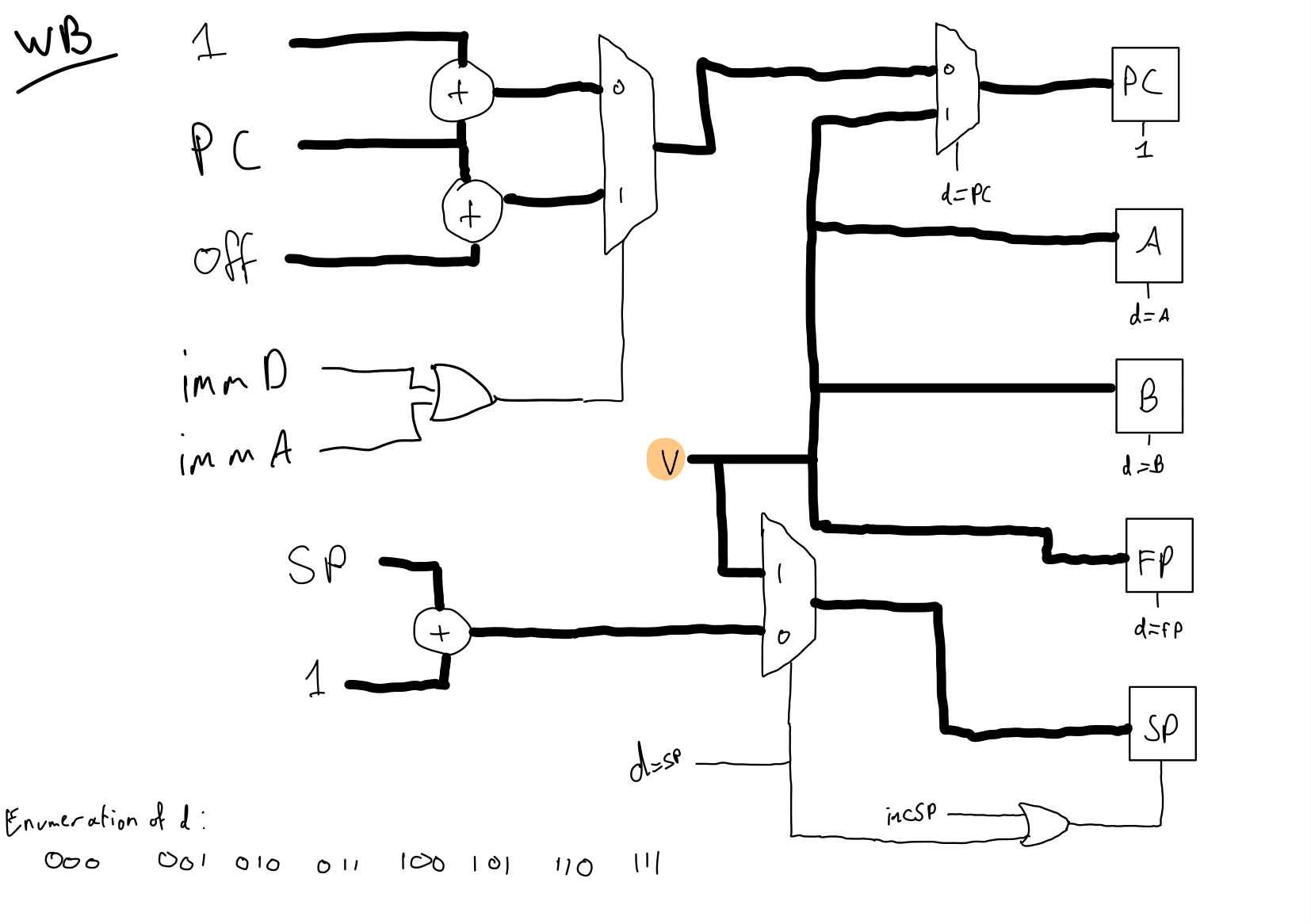

Write-Back (WB)

Phase 3 - IC-Level Implementation Design

Click to see the full-detail PDF!

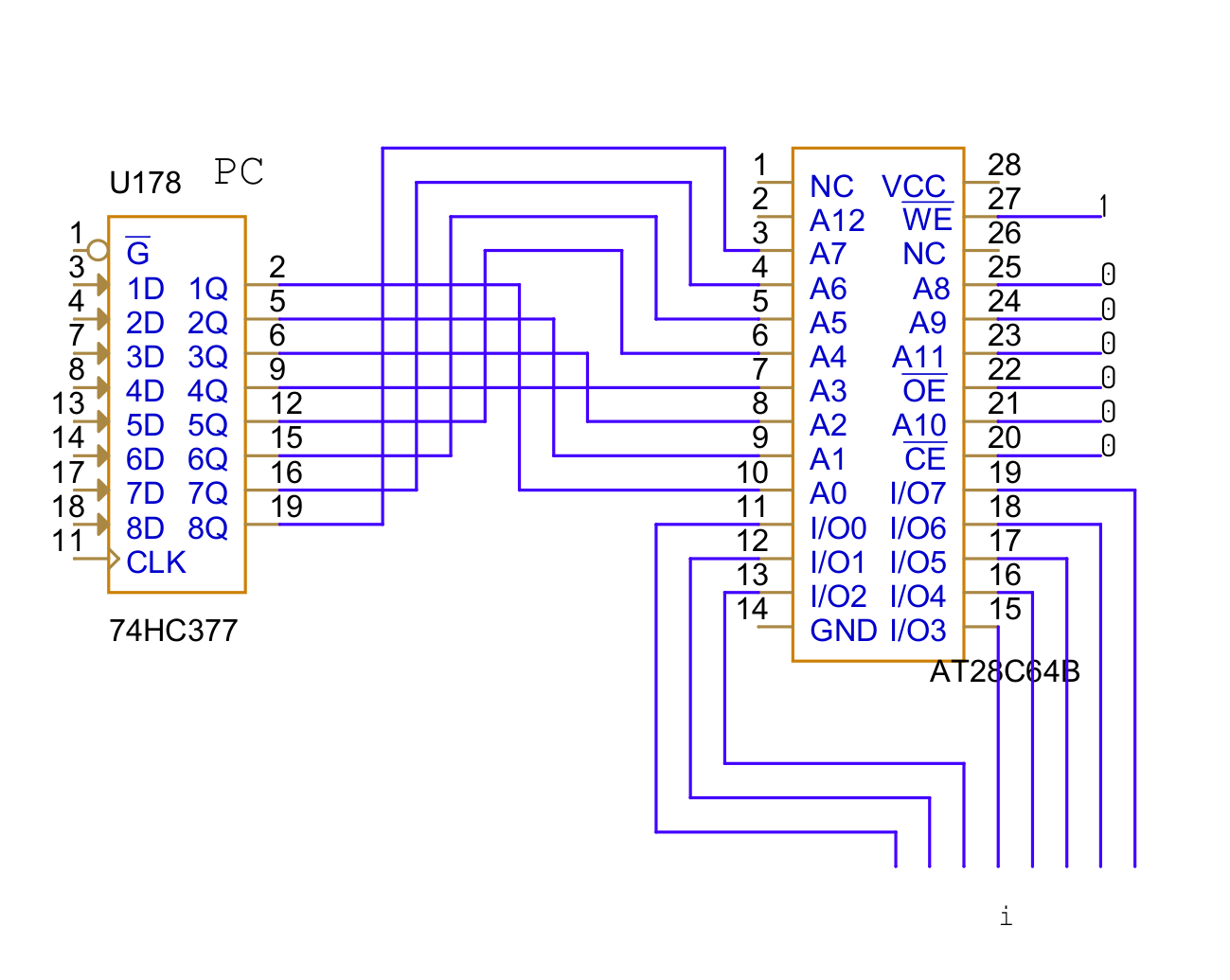

Instruction Fetch (IF)

Instruction Decode (DEC)

Arithmetic Logic Unit (ALU)

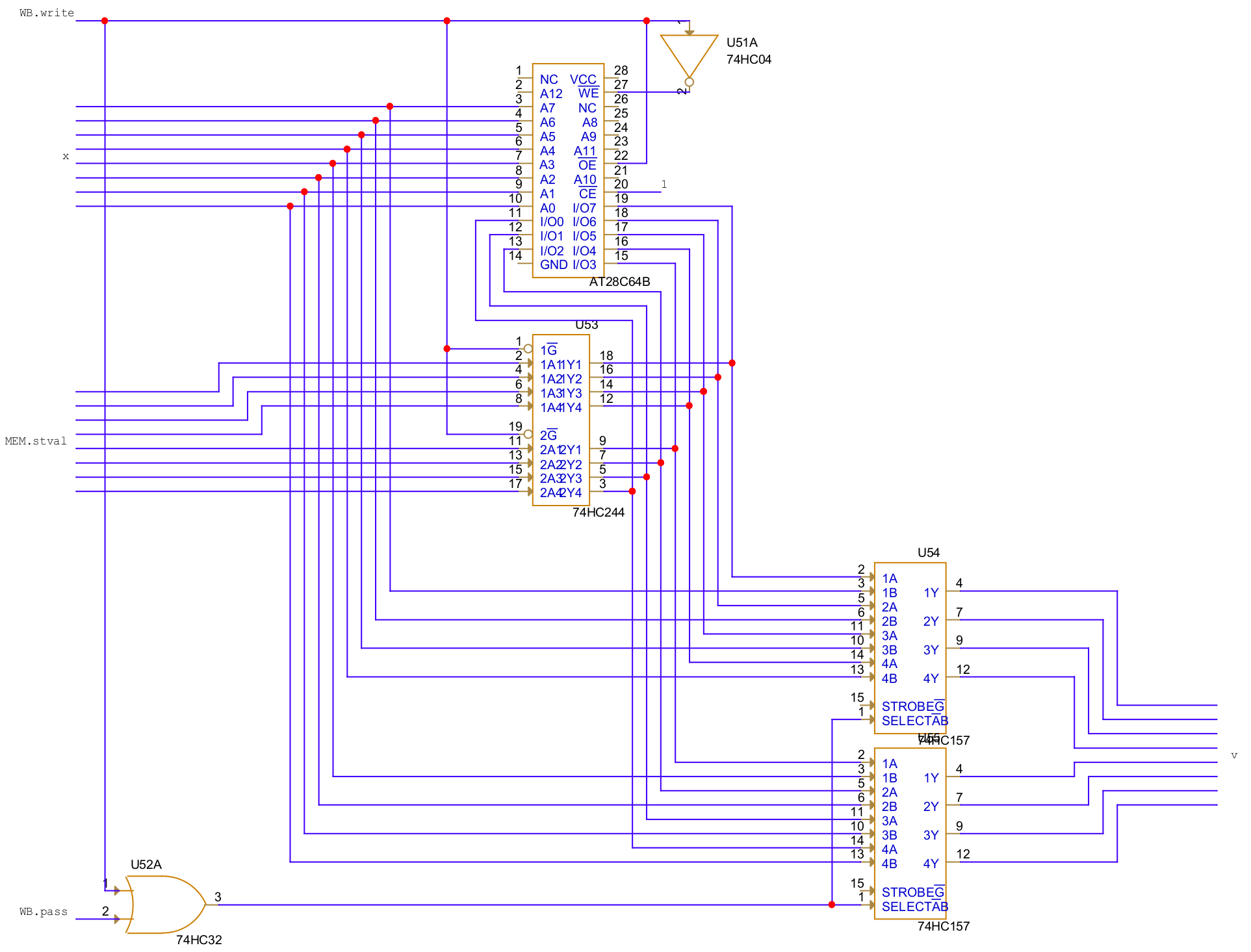

Data Memory Access (MEM)

Write-Back (WB)

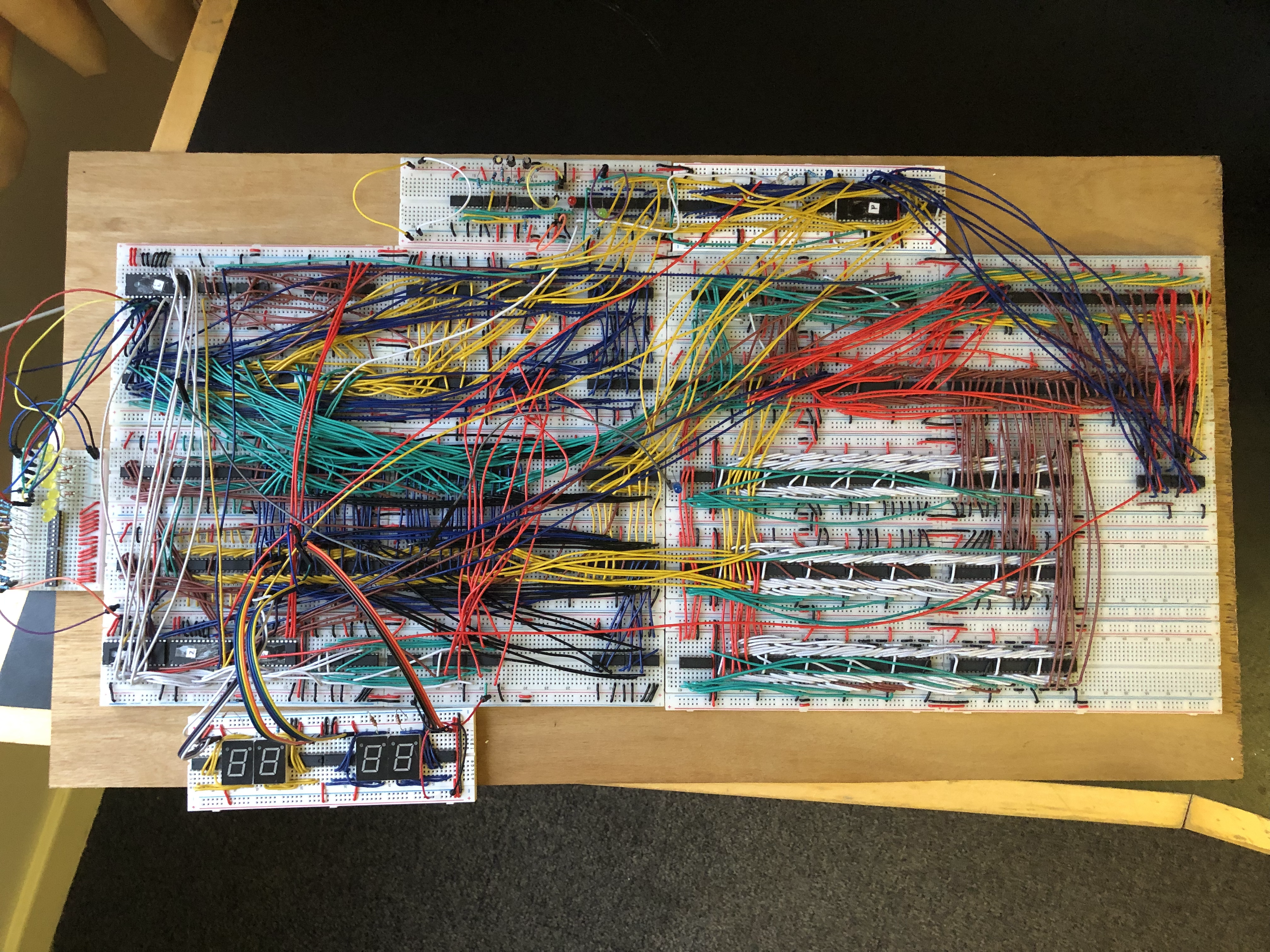

Phase 4 - Breadboarding

Full Board